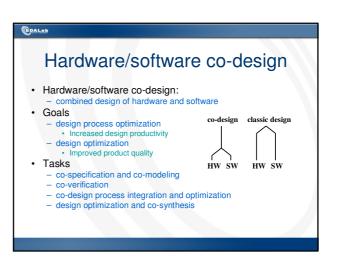

# Co-design advantages Explore different design alternatives in the architectural design space Tune HW to SW and vice-versa Reduce the system design time Support coherent design specification at the system-level Facilitate the re-use of HW and SW parts Provide integrated environment for the synthesis and validation of HW and SW components

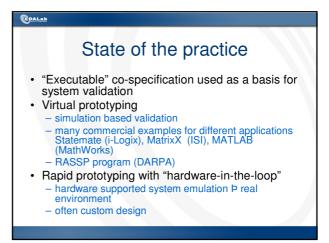

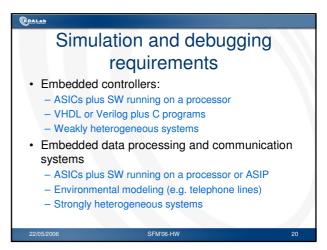

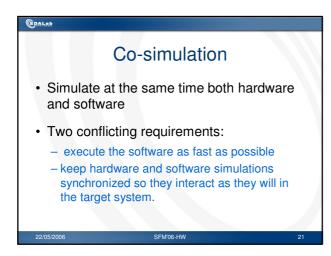

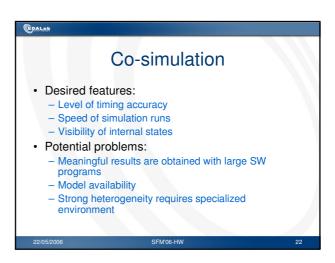

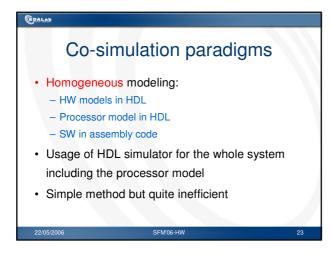

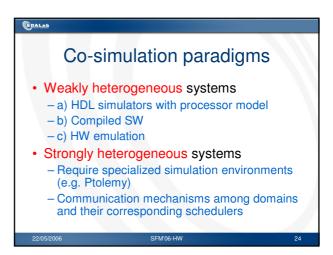

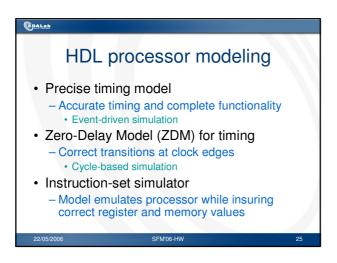

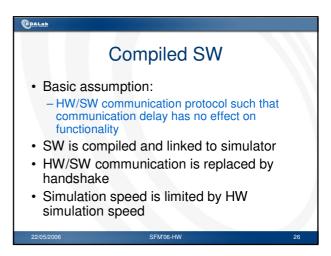

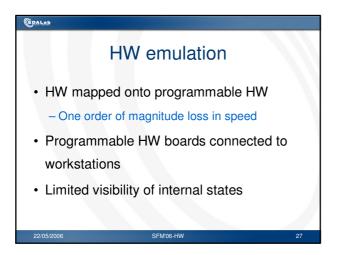

#### State of the practice Co-simulation as a support of design (process) integration extension of simulation techniques to combined simulation of hardware and software components allows permanent control of hardware and software component consistency supports early validation of reused component integration Integration validation more costly with increasing level of detail current focus on co-simulation for lower levels of a design simulation with models of specific processors, memories, busses, ... reduction of accuracy mainly to improve simulation performance examples: Mentor Seamless CVS, Viewlogic Eagle

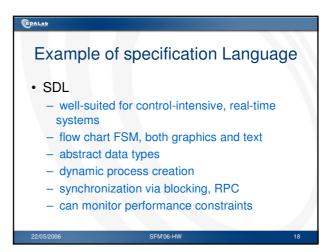

## Example of specification Language • StateCharts, SpecCharts - graphical FSM of states and transitions - addition of hierarchical states for modeling complex reactive behaviors - SpecCharts adds • behavioral completion • exceptions - may attach VHDL code to states and transitions arcs - extended with arithmetics - Easy to use for control-dominated systems

```

Process example

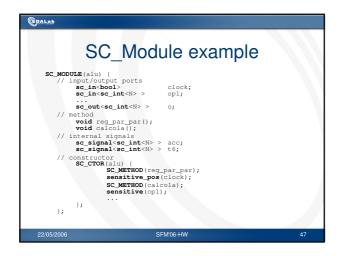

Sc_MODULE(my_module) {

// ports declaration

sc_in<int> a;

sc_in<bol> b;

sc_out<int> x;

// signals declaration

sc_signal<bol> c;

// process declaration

void my_method_proc();

// constructor

Sc_CTOR(my_module) {

// process record

SC_METHOD (my_method_proc);

// sensitivity list declaration

);

);

22/05/2006 SFMO6-HW 49

```

```

Simulation kernel

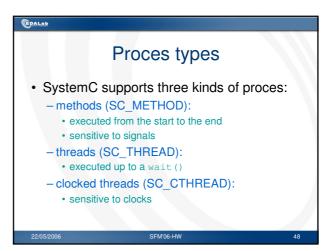

SystemC scheduler works as follows:

all clock signals are updated

all SC_METHOD's and SC_THREAD's with modified input values are executed

all SC_CTHREAD's which must be executed are inserted into a queue

Steps 2 and 3 are repeated up a fixed point

SC_CTHREAD's on queue are executed

increase execution time and goto 1

```

### Port and signal types • sc\_int<n> e sc\_uint<n> • sc\_bigint<n> e sc\_biguint<n> • sc\_bit • sc\_logic • sc\_bv<n> e sc\_lv<n> • sc\_fixed e sc\_ufixed • sc\_fix e sc\_ufix • end user self defined structures

```

Port and signal types example

• sc_in<port_type>;

-// input port of type port_type

• sc_out<port_tipe> x[32];

-// output port ranging from x[0] to x[31] of type port_type

• sc_signal<port_type> i[4];

-// signal ranging from i[0] to i[3] of type port_type

```

```

Synchronous D-flip-flop

// dff.h

#include "systemc.h"

SC_MODULE(dff) { //module declaration

sc_in<bool> clock; //input declaration

sc_in<bool> din;

sc_out<bool> dout; //output declaration

void doit();{

dout = din;

}

SC_CTOR(dff) {

// declaration of a SC_METHOD

// process sensitive to clock

SC_METHOD(doit);

sensitive_pos(clock);

};

};

22052006 SFMOG-HW 53

```

```

Asynchronous D-flip-flop

// dffa.h

#include "systemc.h"

SC_MODULE(dffa) {  //module declaration

sc_in<bol> clock;  //input declaration

sc_in<bol> clock;  //sinput declaration

sc_in<bol> dout;  //output declaration

void do_ffa(); {

if (reset) {

dout = false;

}else if (clock.event()) {

dout = din; }

}

SC_CTOR(dffa) {

SC_METHOD(do_ffa);

sensitive_pos(clock);

};

22052006 SFM06-HW 54

```

```

Serial/serial register

// reg_ser_ser.h

#include "systemc.h"

#define N 8

SC_MODULE(reg_ser_ser) {

sc_in-bool> clock;

sc_in-bool> clock;

sc_out<br/>bool> o;

void register_ser_ser();

SC_CTOR(reg_ser_ser) {

SC_METHOD (register_ser_ser);

sensitive_pos(clock);

};

};

22/05/2006 SFMOG-HW 57

```

```

Parallel/serial register

// reg_par_ser.h

#include "systemc.h"

#define N 8

SC_MODULE(reg_par_ser) {

sc_in<bol>    i0;

sc_

```

```

SC_CTOR(alu) {

SC_METHOD (registro_par_par);

sensitive_pos(clock);

SC_METHOD (calcola);

sensitive(op1);

sensitive(op2);

sensitive(oper);

sensitive(oper);

sensitive(acc);

};

};

2205/2006 SFM'06-HW 64

```

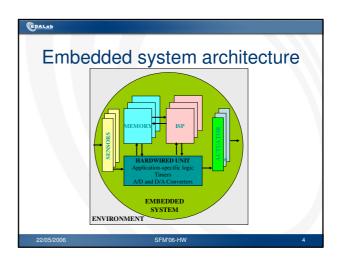

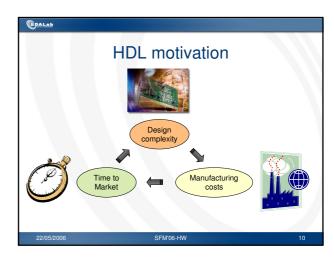

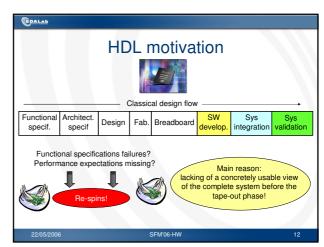

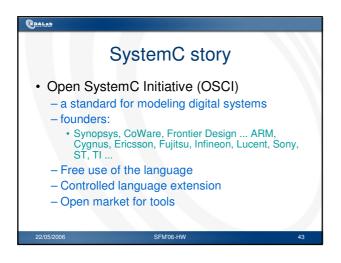

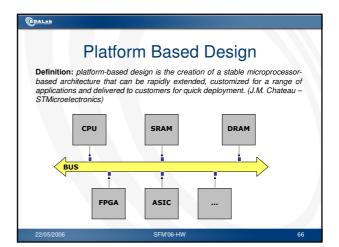

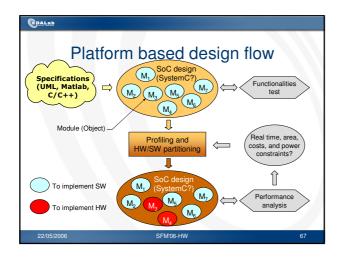

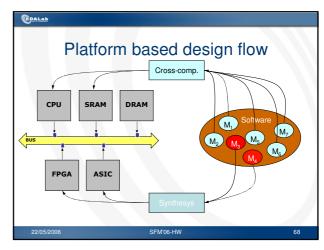

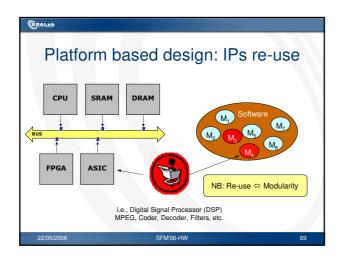

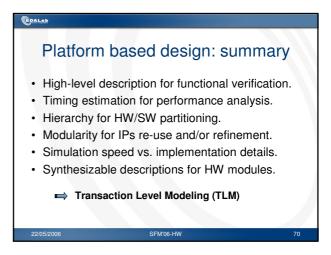

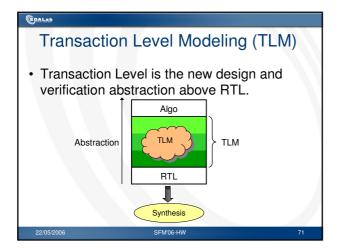

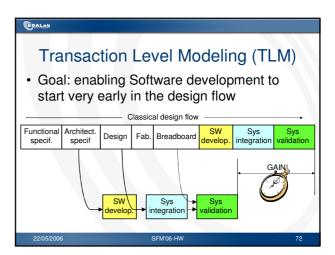

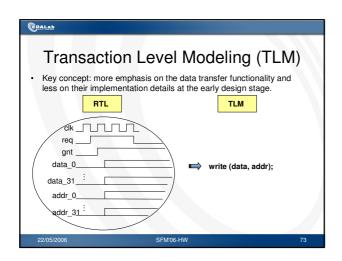

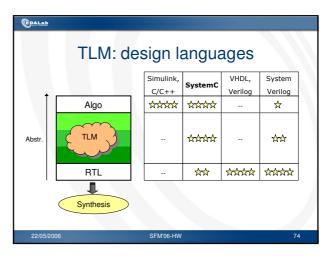

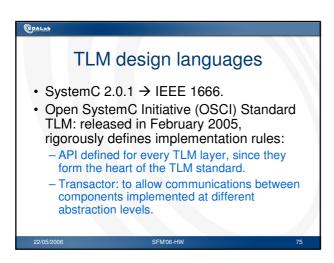

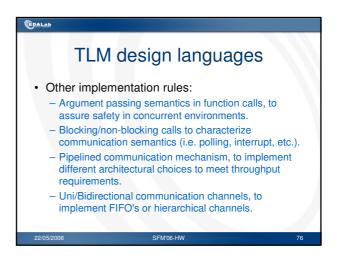

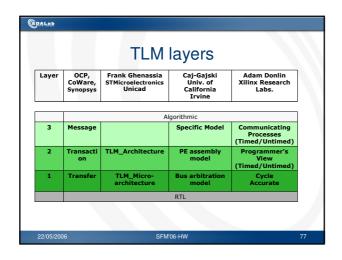

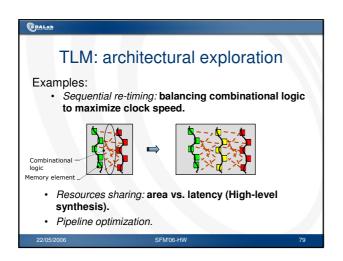

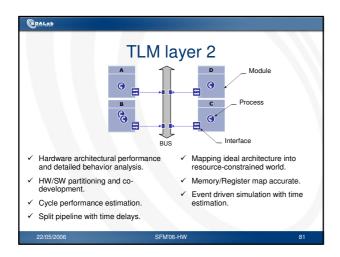

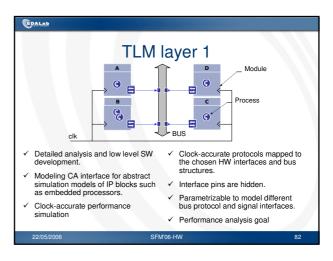

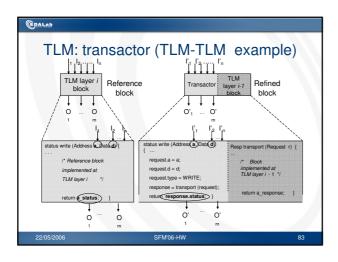

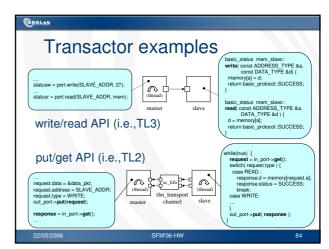

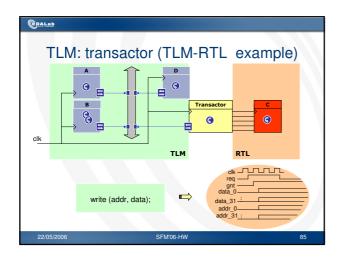

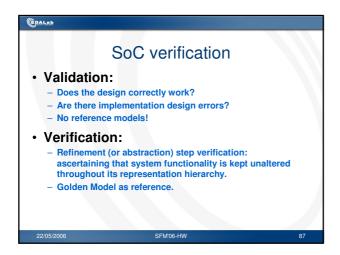

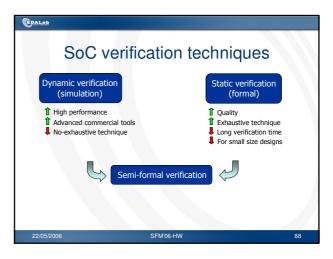

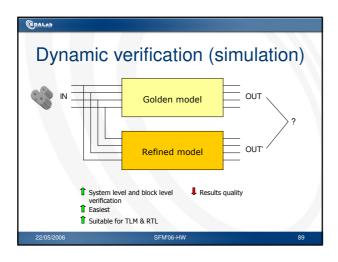

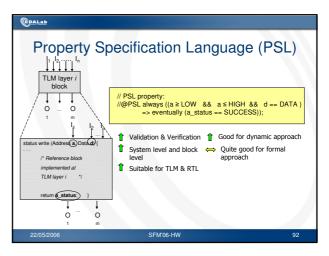

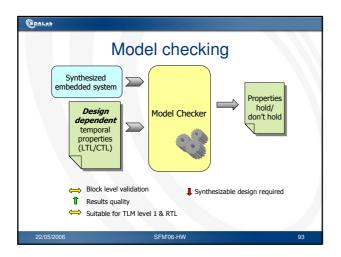

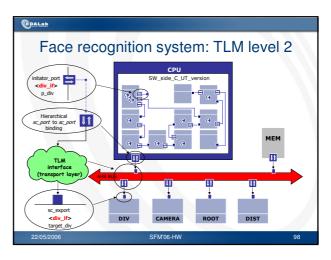

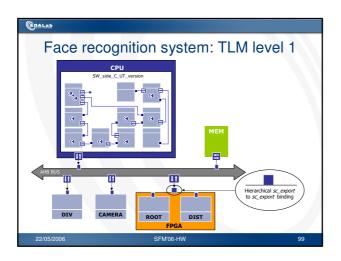

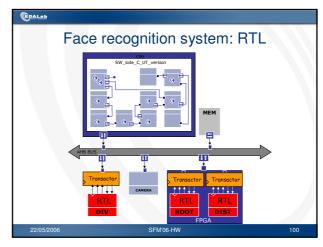

## Platform Based Design (PBD): the customization approach for design complexity, manufacturing cost and time-to-market challenges. Transaction Level Model (TLM) as SoC modeling style. SystemC 2.1 as the de-facto reference languages for SoC design: it rocks! Assertion Based Verification (ABV) and Property Specification Language (PSL)as the new validation and verification trend. Dynamic approach for system level verification and static approach for block level verification