# **Automatic Test Pattern Generation**

Rolf Drechsler, Görschwin Fey University of Bremen

drechsle@informatik.uni-bremen.de

#### **Outline**

- Introduction/Motivation

- Preliminaries

- Circuit, Fault Model, Test Pattern Generation

- Proof techniques

- Boolean satisfiability, BDD, SAT, Circuit to SAT Conversion

- SAT-based ATPG

- Problem description

- Multi-valued Encoding

- Variable Selection

- Experimental Results

- Conclusions

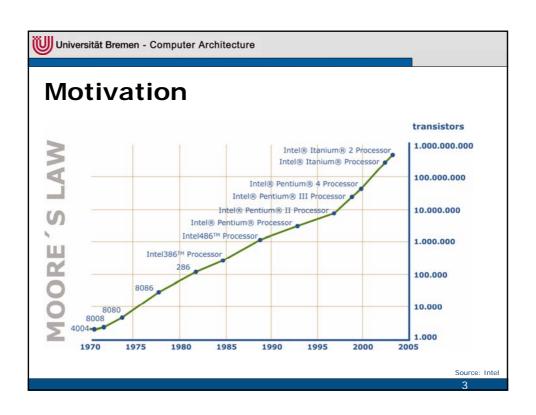

### **Motivation**

- Increasing size of circuits

- Post-production test is a crucial step:

- Have there been problems during production?

- Does the circuit contain faults?

- · Test patterns are applied

### **Motivation**

- Test pattern generation happens at the Boolean level

- Classical ATPG algorithms reach their limits

- ➤ There is a need for more efficient ATPG tools!

5

#### **Circuits**

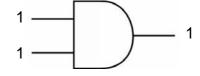

- Basic gates

- AND, OR, EXOR, NOT

#### **Fault Model**

- Model "realistic" fault

- Physical faults or defects at the Boolean level

- Simplified assumption

- · Based on netlist

- · Static or dynamic

- Here: static only

7

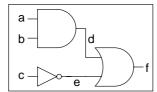

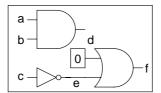

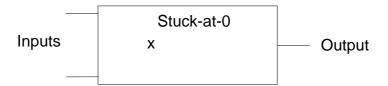

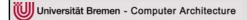

#### **Stuck-at Fault Model**

- Single line is assumed to have a fixed value (0 or 1)

- Example: stuck-at 0 fault at line d correct faulty

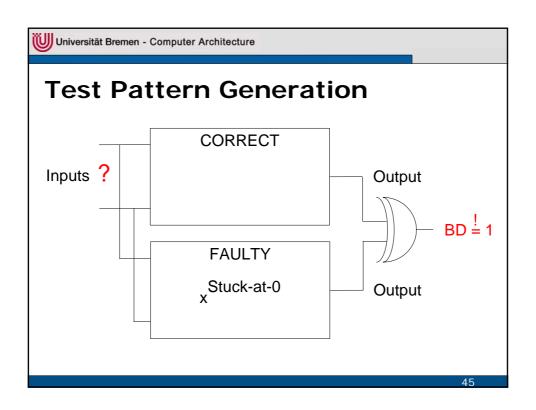

#### **Test Pattern Generation**

Physical defects are modeled on the Boolean level

Automatic Test Pattern Generation (ATPG)

**Given:** Circuit C and Fault-Model F **Objective:** Calculate test patterns for faults in C with respect to F

9

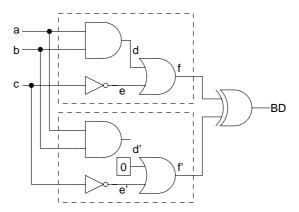

#### **Boolean Difference**

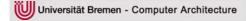

BD of faulty and fault free circuit

#### **Fault Classification**

- If there is a test, the fault is *testable*.

- If there does not exist a test, the fault is redundant.

- Decision is NP complete.

11

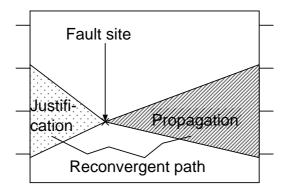

### ATPG: D-Algorithm

- An error is observed due to differing values at a line in the circuit with or without failure. Such a divergence is denoted by values D or D´ to mark differences 1/0 or 0/1, respectively.

- Instead of Boolean values, the set {0,1,D,D´} is used to evaluate gates and carry out implications.

- A gate that is not on a path between the error and any output does never have a D-value.

- A necessary condition for testability is the existence of a path from the error to an output, where all intermediate gates either have a D-value or are not assigned yet. Such a path is called a potential D-chain.

- A gate is on a D-chain, if it is on a path from the error location to an output and all intermediate gates have a D-value.

#### **General Structure**

Justification and Propagation

10

#### **Improvements**

- PODEM: only branch on inputs

- FAN: branching on fanout stems

- SOCRATES: learning

- HANIBAL: recursive learning

- Alternative: SAT-based

- Formulation based on formal techniques

- Proof techniques: BDD and SAT

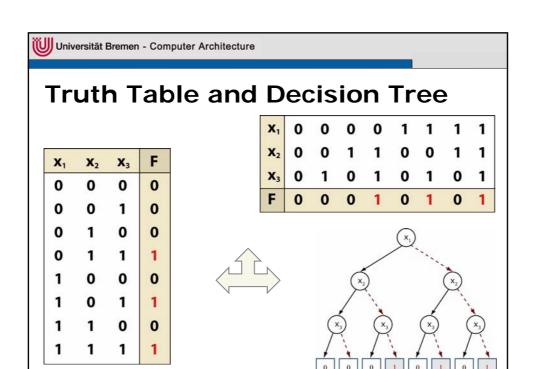

# Representation

- Truth table

- SoP (DNF) and PoS (CNF)

- Examples

- Sum-of-products  $F = x_1'x_2x_3 + x_1x_2'x_3 + x_1x_2x_3$

- Product-of-sums  $F = (x_1 + x_2 + x_3) (x_1 + x_2 + x_3') (x_1 + x_2' + x_3) (x_1' + x_2 + x_3) (x_1' + x_2' + x_3)$

- Decision tree

| <b>X</b> <sub>1</sub> | X <sub>2</sub> | <b>X</b> <sub>3</sub> | F |

|-----------------------|----------------|-----------------------|---|

| 0                     | 0              | 0                     | 0 |

| 0                     | 0              | 1                     | 0 |

| 0                     | 1              | 0                     | 0 |

| 0                     | 1              | 1                     | 1 |

| 1                     | 0              | 0                     | 0 |

| 1                     | 0              | 1                     | 1 |

| 1                     | 1              | 0                     | 0 |

| 1                     | 1              | 1                     | 1 |

# **Shannon Expansion**

A Boolean function can be expanded by Shannon

$$F(x,y,z) = x' F_{x'} + x F_{x}$$

where  $\boldsymbol{F}_{\boldsymbol{x}'}$  and  $\boldsymbol{F}_{\boldsymbol{x}}$  are positive (negative) cofactors

$$F_{x'} = F(0, y, z), F_x = F(1, y, z)$$

10

# **Synthesis Operations: ITE**

• If-Then-Else-Operator:

$$ITE(F, G, H) = FG + F'H$$

- Boolean operations over ITE arguments can be expressed as ITE of F, G, and constants

- Example: AND(F, G) = ITE(F, G, 0)

- Computation of Boolean operations is based on the Shannon expansion:

$$ITE(F,G,H) = ITE(x, ITE(F_{x'},G_{x'},H_{x'}), ITE(F_{x},G_{x},G_{x}))$$

# **Properties**

- Efficient implementation

- Compact representation for many Boolean functions

- Polynomial manipulation algorithms

- · Sensitive to variable ordering

- NP-complete problem

- Dynamic variable ordering

23

# **Function Representation**

- · BDD-based representation of

- functions (with don't cares)

- relations

- minterms, cubes

- sets (of sets)

- state machines

- ...

- Common features of all successful BDD-based representations

#### **Simulation**

- Application of values

- · Fast computation

- linear time

- · New evaluation for each input pattern

- <u>Complete</u> simulation only feasible for small circuits

- exponential in the number of inputs

25

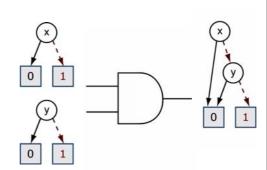

# **Symbolic Simulation**

- Application of variables

- One computation for all input patterns in parallel

- Construction of diagrams for each gate

- synthesis operations

- · Size of diagrams

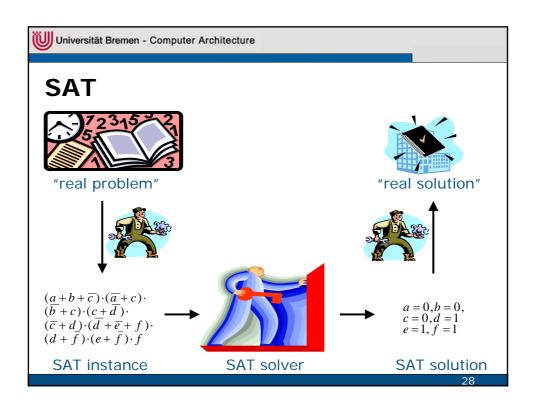

#### **SAT**

- · Often all patterns are not needed

- · A single test-vector is sufficient

- · Construction of satisfying assignment

- <u>SAT-problem</u>: For a given Boolean function f find an assignment a, such that f(a) = 1 or prove that such an assignment does not exist.

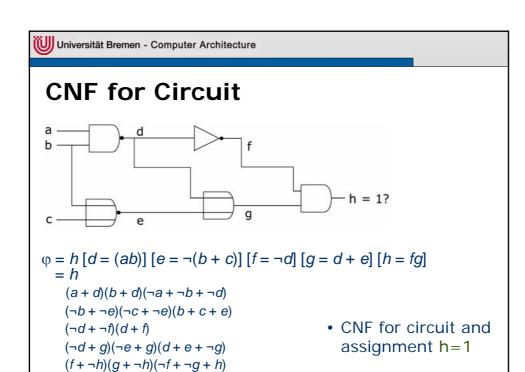

### **CNF** of a Gate

# **SAT Solving**

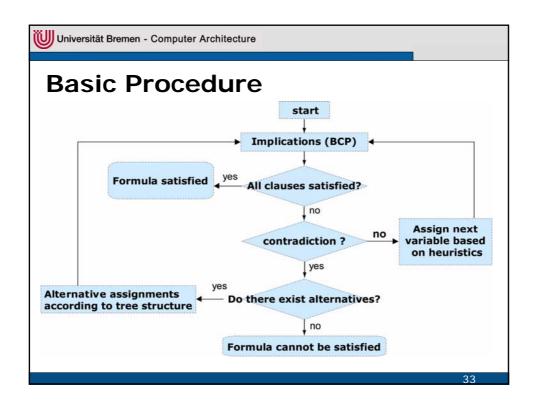

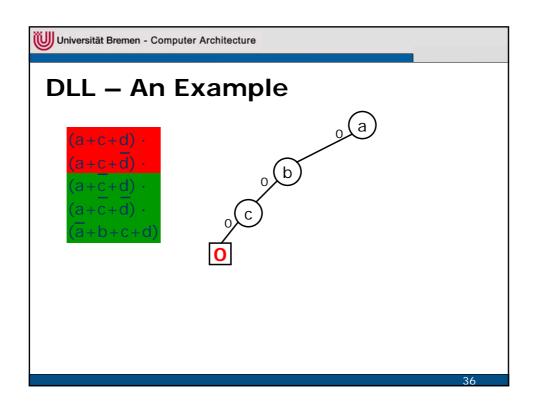

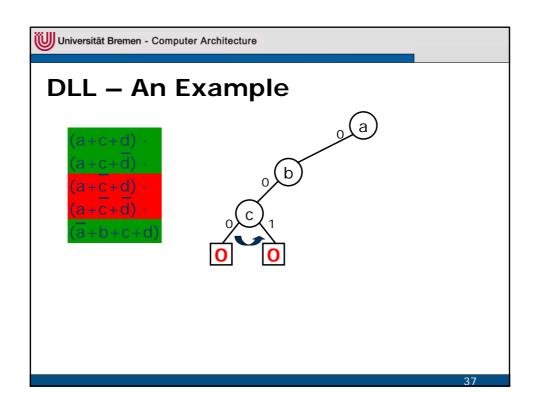

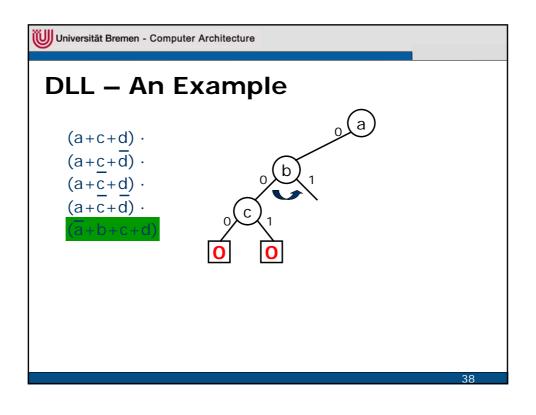

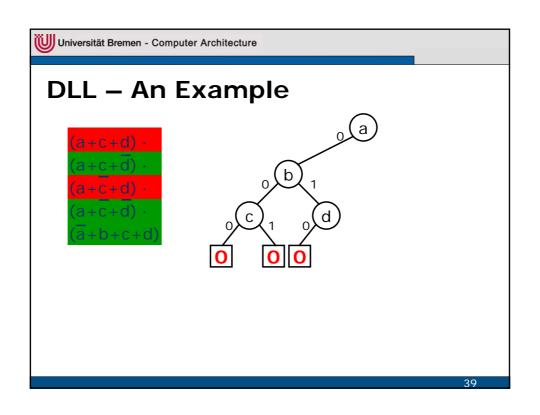

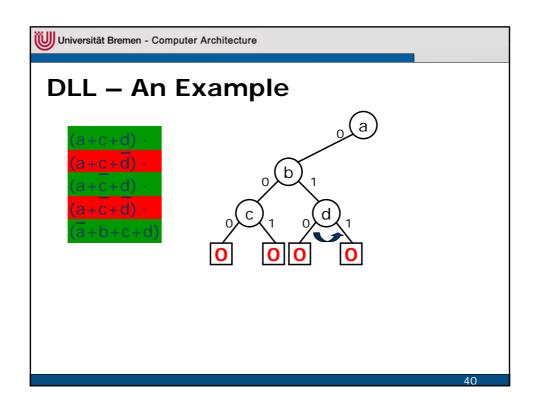

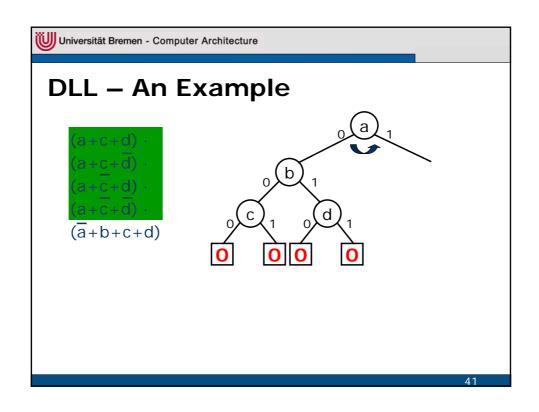

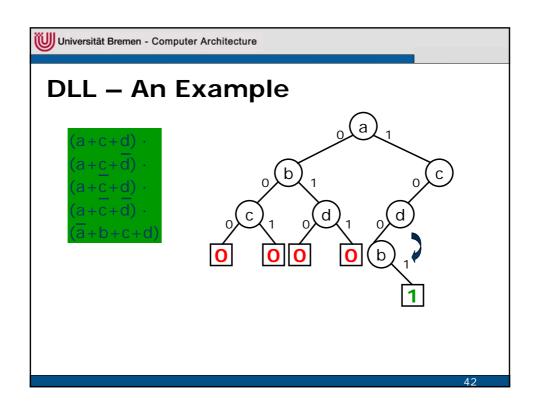

- Most Algorithms are based on DLL procedure

- Overall flow

- Assign variables in the CNF

- If a contradiction occurs backtrack

## **Implications**

• Unit clause: Only one unspecified literal

$$\begin{pmatrix}

\neg a + b + \neg c \\

\parallel & \parallel \\

1 & 0

\end{pmatrix} \Rightarrow c = 0$$

- Boolean constraint propagation (BCP) is based on iteration of unit clause rule

- BCP corresponds to implications on the net list

- Fast implementation, since CNF is very regular

# **Reasons for SAT Efficiency**

- Implications

- Analysis of backtracks

- · Decision heuristics

- Conflict learning

- Instance grows

- · Non-chronological backtracking

- Data structure

- CNF

- Circuit

### **BDDs versus SAT**

- · BDDs consider all solutions

- SAT finds single solution

- · Backtrack tree similar to BDD structure

- Advanced SAT techniques:

- Variable selection strategies

- Efficient implementations

- Engineering

- Implications

- Conflict analysis

43

#### **Motivation for SAT-based ATPG**

- Substantial improvements in SAT solving

- ▶ Use

- Advanced SAT techniques

- In combination with structural information

#### For

- Large industrial circuits

- In a multi-valued domain

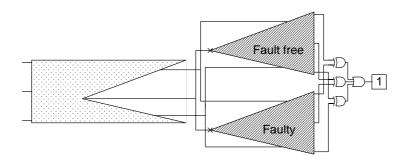

# **SAT-based ATPG**

- Input: Circuit C, Fault F

- Fault modeling:

BD between fault free and faulty circuit

- 2. Translate into CNF

- 3. Use SAT solver to calculate solution

- Output: Classification of F, Testvector T

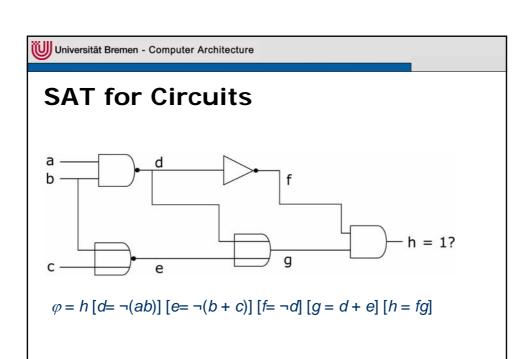

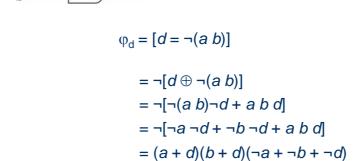

# **Circuit** → **CNF**

- AND-gate:  $(c'+d'+e) \cdot (c+e') \cdot (d+e')$

- OR-gate:  $(a+b+d') \cdot (a'+d) \cdot (b'+d)$

- Linear size conversion

47

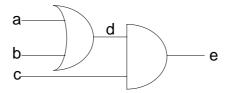

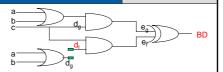

### **Use of Structural Information**

Influenced circuit parts

#### **Create Instance**

• Build circuit structure accordingly

49

#### **CNF**

- $$\begin{split} \bullet \quad & \mathsf{F} = \ (\overline{\mathsf{c}} + \overline{\mathsf{d}}_{\mathsf{g}} + e_{\mathsf{g}}) \cdot (\mathsf{c} + \overline{\mathsf{e}}_{\mathsf{g}}) \cdot (\mathsf{d}_{\mathsf{g}} + \overline{\mathsf{e}}_{\mathsf{g}}) \\ & \cdot \ (\mathsf{a} + \mathsf{b} + \overline{\mathsf{d}}_{\mathsf{g}}) \cdot (\overline{\mathsf{a}} + \mathsf{d}_{\mathsf{g}}) \cdot (\overline{\mathsf{b}} + \mathsf{d}_{\mathsf{g}}) \cdot (\mathsf{d}_{\mathsf{f}}) \\ & \cdot \ (\overline{\mathsf{c}} + \overline{\mathsf{d}}_{\mathsf{f}} + \underline{\mathsf{e}}_{\mathsf{f}}) \cdot (\mathsf{c} + \overline{\mathsf{e}}_{\mathsf{f}}) \cdot (\mathsf{d}_{\mathsf{f}} + \overline{\mathsf{e}}_{\mathsf{f}}) \\ & \cdot \ (\mathsf{e}_{\mathsf{g}} + \mathsf{e}_{\mathsf{f}} + \mathsf{BD}) \cdot (\overline{\mathsf{e}}_{\mathsf{g}} + \mathsf{e}_{\mathsf{f}} + \mathsf{BD}) \cdot (\mathsf{BD}) \\ & \cdot \ (\overline{\mathsf{e}}_{\mathsf{g}} + \mathsf{e}_{\mathsf{f}} + \mathsf{BD}) \cdot (\mathsf{e}_{\mathsf{g}} + \overline{\mathsf{e}}_{\mathsf{f}} + \mathsf{BD}) \cdot (\mathsf{BD}) \end{split}$$

- F is the CNF for circuit with d s-a-1

- Inputs satisfy CNF → can detect fault

- · CNF is linear in circuit size

51

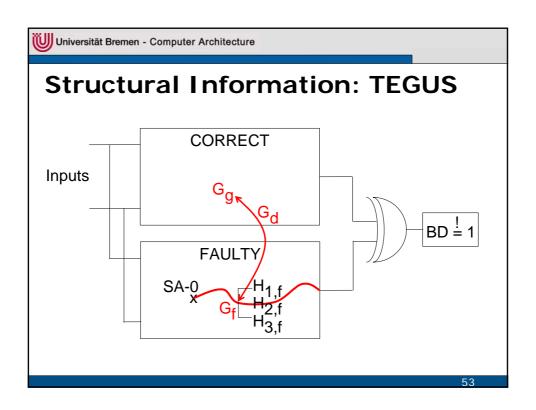

#### Universität Bremen - Computer Architecture

#### Structural information: TEGUS

- · Use approach as in D-algorithm

- Gate G on path between fault and output:

- unfaulty circuit:  $G_g = G(X_g)$

- faulty circuit:  $G_f = G(X_f)$

- G on a D-chain implies

- difference:  $G_d \rightarrow (G_f \neq G_q)$

- at least one successor is on the D-chain:  $G_d \rightarrow (H_{1,d} + ... + H_{k,d})$

### **Features of PASSAT**

- Memory Management

- Advanced SAT techniques

- Problem specific variable selection

- Multi-valued model

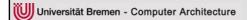

# **Advanced SAT Techniques**

- Built-in techniques from Zchaff

- Conflict based learning

- Non-chronological backtracking

- Event-driven evaluations

- Clever decision heuristics

#### **Variable Selection**

- Use problem specific strategies to chose next decision variable

- Only inputs

- Only fanouts

- Zchaff 's default strategy

- Combined strategy

- First: Only inputs with time-out

- Then: Zchaff's default

57

Out

#### Variable Selection

Use problem specific strategies to chose next decision variable

In

- Only inputs

- Only fanouts

- Zchaff´s default strategy

- Combined strategy

- First: Only inputs with time-out

- Then: Zchaff's default

58

Out

# Variable Selection: p49k

| Heuristic | Cnt | Red | Ab  | Time(s) |

|-----------|-----|-----|-----|---------|

| All       | 0   | 1   | 255 | 3847    |

| Input     | 187 | 67  | 2   | 1787    |

| Fanout    | 0   | 0   | 256 | 2568    |

| Input+All | 187 | 68  | 1   | 2084    |

61

Universität Bremen - Computer Architecture

### **Multi-valued Model**

- Application to industrial circuits

- Allow for ,Z´ and ,U´ values

- Encode circuit lines by two variables

- Optimize the encoding

### **Multi-valued Model**

Encoding

| Χ | Encode         |     | Interpretation      |

|---|----------------|-----|---------------------|

|   | c <sub>x</sub> | c*x |                     |

| 0 | 0              | 0   | Signal X is 0       |

| 1 | 1              | 0   | Signal X is 1       |

| U | 1              | 1   | Signal X is unknown |

| Z | 0              | 1   | Signal X is at 'Z'  |

|   |                | 1   |                     |

• Clauses for c = a • b

$$\begin{array}{l} (\overline{c}_a + \overline{c}_b + c_c) \cdot (c_a^* + c_b^* + \overline{c}_c^*) \cdot (c_c + \overline{c}_c^*) \cdot \\ (c_a + c_a^* + \overline{c}_c) \cdot (c_b + c_b^* + \overline{c}_c) \cdot (\overline{c}_a^* + \overline{c}_b + c_c^*) \cdot \\ (\overline{c}_a + \overline{c}_b^* + c_c^*) \cdot (\overline{c}_a^* + \overline{c}_b^* + c_c^*) \end{array}$$

62

Universität Bremen - Computer Architecture

# **Multi-valued Model: Encodings**

| S | Х | x |

|---|---|---|

| 0 | a | b |

| 1 | a | Б |

| U | ā | b |

| Z | ā | b |

| S | Х | x |

|---|---|---|

| 0 | a | b |

| 1 | a | b |

| U | ā | Б |

| Z | ā | b |

| S | Х | x        |

|---|---|----------|

| 0 | a | b        |

| 1 | ā | <b>b</b> |

| U | ā | b        |

| Z | a | Б        |

"natural"

# **Multi-valued Model: Encodings**

| circ. | enc. | clauses | cls. % | CNF | CNF % | solve | solve % |

|-------|------|---------|--------|-----|-------|-------|---------|

| p44k  | A    | 174,083 |        | 43  |       | 15    |         |

| Piik  | В    | 220,493 |        | 52  | 121   | 79    | 527     |

|       | ь    | 220,493 | 121    | 52  | 121   | 19    | 521     |

| p88k  | A    | 33,406  |        | 8   |       | 4     |         |

| _     | В    | 41,079  | 123    | 10  | 125   | 7     | 175     |

|       |      |         |        |     |       |       |         |

65

# **Experimental Results**

|       | Atalar | nta   | PASSA | T    |

|-------|--------|-------|-------|------|

| circ. | fs     | no fs | Eqn   | SAT  |

| c6288 | 0,75   | 49,43 | 4,78  | 1,79 |

| c7552 | 5,72   | 65,93 | 2,61  | 0,70 |

# Time to classify faults

| circuit | Time for classification |       |      |       |       |

|---------|-------------------------|-------|------|-------|-------|

|         | <0.1                    | 0.1-1 | 1-10 | 10-20 | abort |

| P44k    | 0                       | 57    | 19   | 0     | 0     |

| P49k    | 0                       | 0     | 385  | 0     | 1581  |

| P80k    | 9                       | 207   | 0    | 0     | 0     |

| P88k    | 106                     | 167   | 7    | 0     | 0     |

| P177k   | 137                     | 119   | 58   | 5     | 13    |

| P565k   | 961                     | 440   | 8    | 0     | 0     |

67

#### Multi-valued model: Industrial Circuits

| Circuit | Cnt     | Red   | Ab    | Eqn (s) | SAT (s) |

|---------|---------|-------|-------|---------|---------|

| P44k    | 61230   | 823   | 0     | 17821   | 30797   |

| P77k    | 126338  | 0     | 0     | 1156    | 334     |

| P80k    | 176159  | 5     | 9     | 7420    | 5591    |

| P88k    | 126929  | 2354  | 169   | 2985    | 9044    |

| P99k    | 131913  | 759   | 4548  | 4364    | 36965   |

| P565k   | 1175605 | 26372 | 28343 | 1456    | 3073    |

# **Challenges/Future Work**

- Use of advanced SAT techniques

- incremental SAT

- Optimization of SAT instance

- Boolean reasoning during creation

- · Other fault models

- dynamic model, e.g. path delay faults

69

### **Conclusions**

- SAT for ATPG

- Formulation based on formal techniques

- Use of structural information

- Advanced SAT techniques

- Multi-valued circuits

- · Better run times for "hard" faults

- · Applicable to large industrial circuits